## Programmer's guide

last change on: 2021-02-19

# **CAN - EDCP Programmers guide**

Description of iseg Enhanced Device Control Protocol to access iseg hardware by CAN bus connection

## **Document history**

| Version | Date       | Major changes                                                                                             |

|---------|------------|-----------------------------------------------------------------------------------------------------------|

| 2.6     | 2021-02-17 | Revised flexible groups part Added hardware option bits Added the power nominal, -set, and -measure items |

| 2.5     | 2021-01-12 | Fix "Crate Controller Control" register bit set Crate Enable Active                                       |

| 2.4     | 2020-03-04 | Improve documentation                                                                                     |

| 2.3     | 2020-02-06 | Improve documentation, fixed, Safety Information                                                          |

| 2.2     | 2019-11-08 | Improve documentation, fixed                                                                              |

| 2.1     | 2017-08-30 | Revised                                                                                                   |

| 2.0     | 2016-01-28 | Relayouted documentation                                                                                  |

## **Disclaimer / Copyright**

Copyright © 2021 by iseg Spezialelektronik GmbH / Germany. All Rights Reserved.

This document is under copyright of iseg Spezialelektronik GmbH, Germany. It is forbidden to copy, extract parts, duplicate for any kind of publication without a written permission of iseg Spezialelektronik GmbH. This information has been prepared for assisting operation and maintenance personnel to enable efficient use.

The information in this manual is subject to change without notice. We take no responsibility for any mistake in the document. We reserve the right to make changes in the product design without reservation and without notification to the users. We decline all responsibility for damages and injuries caused by an improper use of the device.

## Safety

This section contains important security information for the installation and operation of the device. Failure to follow safety instructions and warnings can result in serious injury or death and property damage.

Safety and operating instructions must be read carefully before starting any operation.

We decline all responsibility for damages and injuries caused which may arise from improper use of our equipment.

## Depiction of the safety instructions

#### DANGER!

"Danger!" indicates a severe injury hazard. The non-observance of safety instructions marked as "Danger!" will lead to possible injury or death.

#### **WARNING!**

"Warning!" indicates an injury hazard. The non-observance of safety instructions marked as "Warning!" could lead to possible injury or death.

#### **CAUTION!**

Advices marked as "Caution!" describe actions to avoid possible damages to property.

#### INFORMATION

Advices marked as "Information" give important information.

Read the manual.

Attention high voltage!

Important information.

#### Intended Use

The device may only be operated within the limits specified in the data sheet. The permissible ambient conditions (temperature, humidity) must be observed. The device is designed exclusively to control high voltage systems as specified in the data sheet. It must only be used specified in Technical data. Any other use not specified by the manufacturer is not intended. The manufacturer is not liable for any damage resulting from improper use.

## **Qualification of personnel**

A qualified person is someone who is able to assess the work assigned to him, recognize possible dangers and take suitable safety measures on the basis of his technical training, his knowledge and experience as well as his knowledge of the relevant regulations.

## **General safety instructions**

- Observe the valid regulations for accident prevention and environmental protection.

- Observe the safety regulations of the country in which the product is used.

- Observe the technical data and environmental conditions specified in the product documentation.

- You may only put the product into operation after it has been established that the high-voltage device complies with the country-specific regulations, safety regulations and standards of the application.

- The high-voltage power supply unit may only be installed by qualified personnel.

## Important safety instructions

#### DANGER!

This device is part of a high voltage supplying systems. High voltages are dangerous and may be fatal.

USE CAUTION WHILE WORKING WITH THIS EQUIPMENT. BE AWARE OF ELECTRICAL HAZARDS.

Always follow at the minimum these provisions:

- High voltages must always be grounded

- Do not touch wiring or connectors without securing

- Never remove covers or equipment

- Always observe humidity conditions

- Service must be done by qualified personnel only

#### **WARNING!**

RAMP DOWN VOLTAGES!

Before insertion or removal of crate controller, please make sure, that all voltages are ramped down, modules are switched off and power cord is disconnected.

#### **CAUTION!**

When controlling, with software, the high voltage systems, make sure that nobody is near the high voltage or can be injured.

#### INFORMATION

Please check the compatibility with the devices used.

## **Table of Contents**

| Document history                                             | 2        |

|--------------------------------------------------------------|----------|

| Disclaimer / Copyright                                       | 2        |

| Safety                                                       | 3        |

| Depiction of the safety instructions                         | 3        |

| Intended Use                                                 | 4        |

| Qualification of personnel                                   | 4        |

| General safety instructions                                  | 4        |

| Important safety instructions                                | 5        |

| 1 General information                                        | 10       |

| 1.1 Devices covered by this manual                           | 10       |

| 1.2 CAN-Bus Implementation                                   | 11       |

| 2 Crate Controller CC24/23                                   | 12       |

| 2.1 Data types                                               | 12       |

| 2.2 Access rights                                            | 12       |

| 2.3 NMT CAN commands (broadcast messages)                    | 12       |

| 2.4 Crate Controller commands                                | 13       |

| 2.4.1 Crate Controller Uptime                                | 13       |

| 2.4.2 Crate Controller Serial Number                         | 13       |

| 2.4.3 Crate Controller Firmware Release                      | 13       |

| 2.4.4 Crate Controller Firmware Name                         | 13       |

| 2.4.5 Crate Controller Article Description                   | 14       |

| 2.4.6 Crate Controller Control 2.4.7 Crate Controller Status | 14<br>16 |

| 2.4.8 Crate Controller Event Status                          | 17       |

| 2.4.9 Crate Controller Event Mask                            | 17       |

| 2.4.10 Crate Controller Fan Speed Percent                    | 18       |

| 2.4.11 Crate Power On/Off                                    | 18       |

| 2.4.12 Crate Chassis Identification                          | 18       |

| 2.4.13 Crate Backplane Type                                  | 19       |

| 2.4.14 Crate Temperature Sensor                              | 20       |

| 2.4.15 Crate Supply Measurement                              | 20       |

| 2.4.16 Crate Supply Nominal                                  | 20       |

| 2.5 Statistic registers                                      | 21       |

| 2.5.1 CAN Bus Received                                       | 21       |

| 2.5.2 CAN Bus Receiver Overrun 2.5.3 CAN Bus Transmitted     | 21<br>21 |

| 2.5.4 CAN Bus Transmit Buffer Full                           | 22       |

| 2.5.5 CAN Bus Dropped                                        | 22       |

| 2.5.6 CAN Bus Error                                          | 22       |

| 2.5.7 CAN Bus Throttle                                       | 22       |

| 2.5.8 CAN Bus Status                                         | 23       |

| 2.5.9 CAN Bus Disabled                                       | 23       |

| 2.5.10 CAN Bus Bitrate                                       | 23       |

| 2.6 Examples                                                 | 24       |

| 3 Commands for High Voltage Devices                          | 25       |

| 3.1 General information                                      | 25       |

| 3.2 General settings and options                             | 25       |

| 3.3 Op | peration principle                                                                                                                                                                                          | 26       |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|        | 3.1 Remote interface control                                                                                                                                                                                | 26       |

|        | 3.2 Channel and Module                                                                                                                                                                                      | 27       |

|        | 3.3 Terminology                                                                                                                                                                                             | 27       |

|        | 3.4 Channel operation modes                                                                                                                                                                                 | 28       |

|        | 3.5 Status and Event generation                                                                                                                                                                             | 29       |

|        | 3.6 Additional current measuring range (Option)                                                                                                                                                             | 29       |

| 3.3    | 3.7 Control and Status items                                                                                                                                                                                | 30       |

|        | 3.3.7.1 Controls                                                                                                                                                                                            | 30       |

|        | 3.3.7.2 Status and events                                                                                                                                                                                   | 30       |

| 2.5    | 3.3.7.3 Event status and event mask                                                                                                                                                                         | 30       |

| 3.3    | 3.8 Summarizing channel characteristics into groups                                                                                                                                                         | 32       |

|        | 3.3.8.1 Set Group                                                                                                                                                                                           | 32       |

|        | 3.3.8.2 Status Group                                                                                                                                                                                        | 32<br>32 |

|        | 3.3.8.3 Monitor Group                                                                                                                                                                                       | 32       |

|        | 3.3.8.4 Timeout Group 3.3.8.5 Responses on events (Soft-Kill features)                                                                                                                                      | 32       |

|        |                                                                                                                                                                                                             |          |

|        | ommunication via Interface                                                                                                                                                                                  | 33       |

| 3.4    | 4.1 Enhanced Device Control Protocol EDCP                                                                                                                                                                   | 33       |

| 2      | 3.4.1.1 Data formats                                                                                                                                                                                        | 35       |

|        | 4.2 CAN Data Frame                                                                                                                                                                                          | 36       |

|        | 4.3 Summary of CAN data frame accesses via the NMT service identifier                                                                                                                                       | 38<br>40 |

| 5.4    | <ul><li>4.4 Summary of CAN data frame accesses via the Front-end-address identifier</li><li>3.4.4.1 List to access of the EDCP made for HV boards up to 255 channels EDCP Single Channel Accesses</li></ul> | 40       |

|        | 3.4.4.1 List to access of the EDCF fliade for AV boards up to 255 channels EDCF single Channel Accesses  3.4.4.2 EDCP Multiple Single Channels Access                                                       | 40       |

|        | 3.4.4.3 Module Access                                                                                                                                                                                       | 44       |

|        | 3.4.4.4 EDCP Group Accesses                                                                                                                                                                                 | 46       |

|        | 3.4.4.5 Important DCP Module Access                                                                                                                                                                         | 47       |

| 2 F D. |                                                                                                                                                                                                             |          |

|        | escription of data information per DATA_ID in EDCP                                                                                                                                                          | 48       |

| 5.5    | 5.1 EDCP Single Access 3.5.1.1 Channel status (single/multiple single read-write access)                                                                                                                    | 48<br>48 |

|        | 3.5.1.1 Channel status (single/multiple single read-write access)  3.5.1.2 Channel status32 (single/multiple single read-write access)                                                                      | 48       |

|        | 3.5.1.3 Channel control: (single write- and single/ multiple single read-write access)                                                                                                                      | 51       |

|        | 3.5.1.4 Channel control32: (single write- and single/ multiple single read-write access)                                                                                                                    | 51       |

|        | 3.5.1.5 Channel event status (single write- and single/ multiple single read-write access)                                                                                                                  | 52       |

|        | 3.5.1.6 Channel event status32 (single write- and single/ multiple single read-write access)                                                                                                                | 53       |

|        | 3.5.1.7 Channel event mask (single write- and single/ multiple single read-write access)                                                                                                                    | 55       |

|        | 3.5.1.8 Channel event mask32 (single write- and single/ multiple single read-write access)                                                                                                                  | 55       |

|        | 3.5.1.9 Delayed trip time                                                                                                                                                                                   | 57       |

|        | 3.5.1.10 Delayed trip action (single/ multiple single read-write access)                                                                                                                                    | 57       |

|        | 3.5.1.11 External channel inhibit                                                                                                                                                                           | 58       |

|        | 3.5.1.12 VoltageRampPriority (single write- and single/ multiple single read-write access)                                                                                                                  | 58       |

|        | 3.5.1.13 Set voltage (single write- and single/ multiple single read-write access)                                                                                                                          | 59       |

|        | 3.5.1.14 Set current / trip (single write- and single/ multiple single read-write access)                                                                                                                   | 59       |

|        | 3.5.1.15 Voltage measurement (single/ multiple single read-write access)                                                                                                                                    | 60       |

|        | 3.5.1.16 Current measurement (single/ multiple single read-write access)                                                                                                                                    | 60       |

|        | 3.5.1.17 Voltage bounds (single write- / single/ multiple single read-write access)                                                                                                                         | 61       |

|        | 3.5.1.18 Current bounds (single write- / single/ multiple single read-write access)                                                                                                                         | 61       |

|        | 3.5.1.19 Nominal voltage (single/ multiple single read-write access)                                                                                                                                        | 62       |

|        | 3.5.1.20 Nominal current (single/ multiple single read-write access)                                                                                                                                        | 62       |

|        | 3.5.1.21 Nominal power (single/ multiple single read-write access)                                                                                                                                          | 62       |

|        | 3.5.1.22 Current measurement range (single/ multiple single read-write access)                                                                                                                              | 63       |

|        | 3.5.1.23 VoltageBottom (single/ multiple single read-write access)                                                                                                                                          | 63       |

|        | 3.5.1.24 VCT Coefficient (single/ multiple single read-write access)                                                                                                                                        | 64       |

|        | 3.5.1.25 Temperature external (single/ multiple single read-write access)                                                                                                                                   | 64       |

|        | 3.5.1.26 Resistor external (single/ multiple single read-write access)                                                                                                                                      | 65<br>65 |

|        | 3.5.1.27 VoltageRampSpeedUp (single write- / single/ multiple single read-write access)                                                                                                                     | 65<br>65 |

|        | 3.5.1.28 VoltageRampSpeedDown (single write- / single/ multiple single read-write access) 3.5.1.29 CurrentRampSpeedUp (single write- / single/ multiple single read-write access)                           | 65<br>66 |

|        | 3.5.1.29 CurrentRampSpeedOp (single write-7 single/ multiple single read-write access)  3.5.1.30 CurrentRampSpeedDown (single write- / single/ multiple single read-write access)                           | 66       |

|        | 3.5.1.30 Currentkampspeedbown (single write- / single/ multiple single read-write access)  3.5.1.31 VoltageRampSpeedMin (single write- / single/ multiple single read-write access)                         | 66       |

|        | 3.5.1.32 VoltageRampSpeedMax (single write- / single/ multiple single read-write access)                                                                                                                    | 67       |

|        | 5.552 . Takabanan papadaman (ambid write / ambid/ mattiple ambid read write access)                                                                                                                         | 07       |

| 3.5.1.33 CurrentRampSpeedMin (single write- / single/ multiple single read-write access)        | 67  |

|-------------------------------------------------------------------------------------------------|-----|

| 3.5.1.34 CurrentRampSpeedMax (single write- / single/ multiple single read-write access)        | 67  |

| 3.5.1.35 PowerSet (single write- / single/ multiple single read-write access)                   | 68  |

| 3.5.1.36 PowerMeasure (single/ multiple single read-write access)                               | 68  |

| 3.5.1.37 Output mode (single/ multiple single read-write access)                                | 69  |

| 3.5.1.38 Output polarity (single/ multiple single read-write access)                            | 69  |

| 3.5.1.39 Output voltage mode (single/ multiple single read-write access)                        | 69  |

| 3.5.1.40 Output current mode (single/ multiple single read-write access)                        | 70  |

| 3.5.1.41 Output voltage mode list (single/ multiple single read-write access)                   | 70  |

| 3.5.1.42 Output current mode list (single/ multiple single read-write access)                   | 70  |

| 3.5.1.43 Group number (single/ multiple single read-write access)                               | 71  |

| 3.5.2 EDCP Module Accesses                                                                      | 72  |

| 3.5.2.1 ModuleStatus (module read-write access)                                                 | 72  |

| 3.5.2.2 ModuleStatus32 (module read-write access)                                               | 72  |

| 3.5.2.3 ModuleControl (module write- / read-write access)                                       | 75  |

| 3.5.2.4 ModuleControl32 (module write- / read-write access)                                     | 75  |

| 3.5.2.5 ModuleEventStatus (module write- / read-write access)                                   | 77  |

| 3.5.2.6 ModuleEventStatus32 (single/ multiple single read-write access)                         | 77  |

| 3.5.2.7 ModuleEventMask (module write- / read-write access)                                     | 78  |

| 3.5.2.8 ModuleEventMask32 (module write- / read-write access)                                   | 79  |

| 3.5.2.9 ModuleEventChannelStatus (module write- / read-write access)                            | 80  |

| 3.5.2.10 ModuleEventChannelStatus32 (module write- / read-write access)                         | 80  |

| 3.5.2.11 ModuleEventChannelMask (module write- / read-write access)                             | 81  |

| 3.5.2.12 ModuleEventChannelMask32 (module write- / read-write access)                           | 81  |

| 3.5.2.13 ModuleEventGroupStatus (module write- / read-write access)                             | 82  |

| 3.5.2.14 ModuleEventGroupMask (module write- / read-write access)                               | 83  |

| 3.5.2.15 VoltageRampSpeed (module write- / read-write access)                                   | 84  |

| 3.5.2.16 CurrentRampSpeed – current controlled modules only (module write- / read-write access) | 84  |

| 3.5.2.17 VoltageMax – OPTION (module read-write access)                                         | 85  |

| 3.5.2.17 Voltage Max Of Fior (module read-write access)                                         | 86  |

| 3.5.2.19 Supply24 (module read-write access)                                                    | 86  |

| 3.5.2.20 Supply5 (module read-write access)                                                     | 87  |

|                                                                                                 | 87  |

| 3.5.2.21 BoardTemperature (module read-write access)                                            | 87  |

| 3.5.2.22 Threshold to arm the errors detection (module write / read- write access)              | 88  |

| 3.5.2.23 Serial number (module read-write access)                                               |     |

| 3.5.2.24 Firmware release (module read-write access)                                            | 88  |

| 3.5.2.25 Bit rate (module write- / read-write access)                                           | 88  |

| 3.5.2.26 Firmware Name (module read-write access)                                               | 89  |

| 3.5.2.27 ADC SamplesPerSecond SPS (module write- / read-write access)                           | 90  |

| 3.5.2.28 DigitalFilter (module write- / read-write access)                                      | 90  |

| 3.5.2.29 ChannelNumber (module read access)                                                     | 90  |

| 3.5.2.30 ArticleDescription (module read access)                                                | 91  |

| 3.5.2.31 ModuleOption (module read access)                                                      | 91  |

| 3.5.2.32 ModuleOptionSpec (module read access)                                                  | 93  |

| 3.5.2.33 ModuleCommMode (module write access)                                                   | 94  |

| 3.5.3 EDCP Group Accesses                                                                       | 95  |

| 3.5.3.1 SetGroup                                                                                | 96  |

| 3.5.3.2 StatusGroup                                                                             | 98  |

| 3.5.3.3 MonitoringGroup                                                                         | 100 |

| 3.5.3.4 DelayedTripGroup                                                                        | 102 |

| 3.5.3.5 Request Temperatures and Supplies (group write access)                                  | 104 |

| 3.5.3.6 GroupVoltageLimit – OPTION (module read-write access)                                   | 104 |

| 3.5.3.7 GroupCurrentLimit – OPTION (module read-write access)                                   | 104 |

| 3.5.3.8 VoltageSetAllChannels (group write access)                                              | 105 |

| 3.5.3.9 Current-Trip/Set-AllChannels (group write access)                                       | 105 |

| 3.5.3.10 SetOnOffAllChannels (group write- / read-write access)                                 | 106 |

| 3.5.3.11 SetEmergencyAllChannels (group write- / read-write access)                             | 107 |

| 3.5.3.12 EventStatusVoltageLimitAllChannels (group write- / read-write access)                  | 108 |

| 3.5.3.13 EventStatusCurrentLimitAllChannels (group write- / read-write access)                  | 109 |

| 3.5.3.14 EventStatusCurrentTripAllChannels (group write- / read-write access)                   | 110 |

| 3.5.3.15 EventStatusExternalInhibitAllChannels (group write- / read-write access)               | 111 |

| 3.5.3.16 Set ON / OFF channels extender (group write- / read-write access)                      | 112 |

| 3.5.3.17 Set EMERGENCY channels extender (group write- / read-write access)                     | 113 |

| 5 Manufacturer contact                                                                                         | 125        |

|----------------------------------------------------------------------------------------------------------------|------------|

| 4.5 Appendix E – Literature references                                                                         | 125        |

| save bit                                                                                                       | 124        |

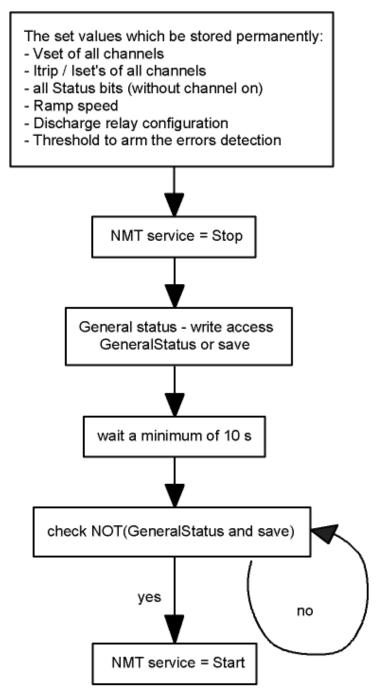

| 4.4 Appendix D – Programming flowchart to store the configurations of the module permanently with help of Gene | eral state |

| 4.3 Appendix C – Programming flowchart to store the settings permanently with help of General state save bit   | 123        |

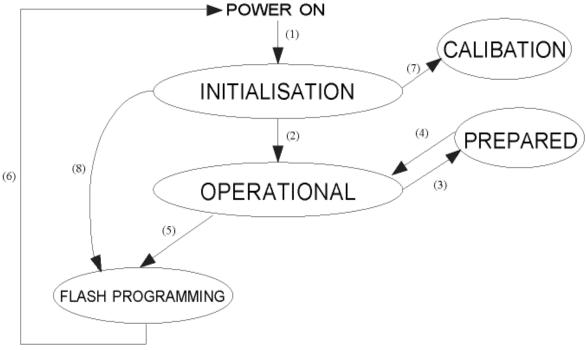

| 4.2 Appendix B – Diagram of operating modes                                                                    | 122        |

| 4.1 A – Shortcuts                                                                                              | 121        |

| 4 Appendix                                                                                                     | 121        |

| 3.5.5.3 Module events                                                                                          | 119        |

| 3.5.5.2 Group events (in preparation)                                                                          | 119        |

| 3.5.5.1 Channel events                                                                                         | 118        |

| 3.5.5 Events                                                                                                   | 118        |

| 3.5.4.2 Log-on / Log-off Front-end device at superior layer (module active- / write access)                    | 116        |

| 3.5.4.1 GeneralStatus (group write- / read-write / active access)                                              | 114        |

| 3.5.4 Important DCP Module Accesses                                                                            | 114        |

## 1 General information

This Manual describes for one the CAN - EDCP crate controller commands and for the other the CAN - EDCP commands for High Voltage Devices.

## 1.1 Devices covered by this manual

All devices described in this manual have in common, that they support the CAN - EDCP (Enhanced device communication protocol for Controller Area Network).

- CC24 is the crate controller card for the 19" master crates with the iCS-2 (iseg Communication Server 2)

- CC23 is the crate controller card for the 19" slave crates

- EHS combines standard or high precision, high voltage sources in 19" format with fix or mixed output polarity, up to 32 channels per module are possible

- EHS FLEX combines standard or high voltage sources in 19" format with fix or mixed output polarity, up to 48 channels per module are possible

- EHS STACK combines standard or high precision, high voltage sources in 19" format with fix or mixed output polarity, up to 16 channels per module are possible

- EBS combines standard, bipolar current sink and high voltage sources in 19" format, up to 24 channels per module are possible

- · EDS combines standard high voltage sources with fix output polarity, up to 48 channels per module are possible

- NHS combines standard or high precision high voltage sources in NIM format with fix or mixed output polarity, up to 6 channels per module are possible

- NHR combines standard or high precision high voltage sources in NIM format with switchable output polarity, up to 4 channels per module are possible

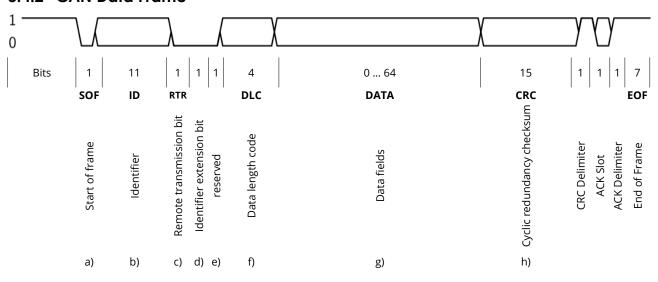

## 1.2 CAN-Bus Implementation

The data frame structure is matched to the message frame of the standard-format according to CAN specification 2.0B.

The data frame of the EDCP will be transferred as data word with n bytes length in the data field of the CAN frame according to the specific demand of the related access. Therefore this results into a Data Length Code (DLC) of the CAN-protocol of n.

The 11 bit identifier of the CAN protocol will be used for addressing of the Front-end devices and classification of data write, data request, data reply and alarm messages.

In following every bit of the 11 bit identifier will be described:

| ID10 (C)          | 1             | Crate controller command                                                   |

|-------------------|---------------|----------------------------------------------------------------------------|

|                   | 0             | High voltage source command                                                |

| ID9 (P)           | 1             | Alarm                                                                      |

|                   | 0             | Normal messages                                                            |

| Notes:            |               |                                                                            |

| ID8 to ID3 (A5A0) | allow the add | dressing of 64 Front-end devices (ID3: Address bit 0;; ID8: Address bit 5) |

| ID2 (NMT)         | 1             | Send a broadcast message defined as network management message (NMT)       |

|                   | 0             | Normal or alarm message                                                    |

| ID1               | 1             | Reply of a data request                                                    |

|                   | 0             | No data request                                                            |

| ID0 (DATA_DIR)    | 1             | Data request                                                               |

|                   | 0             | Data write                                                                 |

That means all "even" CAN-ports (Identifier) are interpreted as 'Write ports' all "odd" CAN ports as 'Read ports'.

Only if the Front-end device is not registered at the controller or if it does not receive valid data during a longer time period (ca. 1 min), then it will actively send the registration frame with DATA\_DIR = 1. The RTR Bit is always set to zero.

In one CAN segment modules with unequal identifier and equal bit rate are allowed only. The factory fixed bit rate is written on the sticker at the side panel.

## 2 Crate Controller CC24/23

## 2.1 Data types

UI1: One byte unsigned integer (8 bit)

CHAR: One ASCII character (8 bit)

UI4: Four byte unsigned integer (32 bit)

R4: Four byte floating point IEEE-754, single precision

All data on the CAN bus is in big endian format, i.e. for UI4 and R4, the highest data byte is transmitted first.

## 2.2 Access rights

R = Read only: the register can only be read

R/W = Read/write: the register can be read and written R/C = Read/clear: the register can be read and cleared

## 2.3 NMT CAN commands (broadcast messages)

The following NMT commands (CAN-ID 0x004) are handled by the Crate Controller:

- NMT\_DATAID\_START (0xC4)

- Switches from stop mode to normal operation

- Message is forwarded to the backplane (and therefore to the modules)

- NMT\_DATAID\_STOP (0xC8)

- Switches from normal operation to stop mode to allow the command NMT\_RESET\_CAN

- Message is forwarded to the backplane (and therefore to the modules)

- NMT\_DATAID\_RESET\_CAN (0xCC)

- Re-initializes all CAN interfaces

- Clears all transmit buffer

- Clears all statistic registers

- Message is forwarded to the backplane (and therefore to the modules)

- Re-initializes the modules CAN interface

- Modules starts to send their Log-On message

A short delay (10 milliseconds) should be kept between the commands NMT\_STOP and NMT\_RESET\_CAN, so that all messages can be forwarded correctly to the modules.

## 2.4 Crate Controller commands

## 2.4.1 Crate Controller Uptime

Crate Controller Uptime 0x1113 UI4 R

This register returns the crate controllers uptime in seconds.

| Access  | CAN-ID | DLC | DATA_ID | Data_3           | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|------------------|--------|--------|--------|

| Request | 0x601  | 2   | 0x1113  |                  |        |        |        |

| Answer  | 0x604  | 6   | 0x1113  | Crate Uptime UI4 |        |        |        |

#### 2.4.2 Crate Controller Serial Number

Crate Controller Serial Number 0x1200 UI4 R

This register returns the crate controllers serial number.

| Access  | CAN-ID | DLC | DATA_ID | Data_3                  | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|-------------------------|--------|--------|--------|

| Request | 0x601  | 2   | 0x1200  |                         |        |        |        |

| Answer  | 0x604  | 6   | 0x1200  | Crate Serial Number UI4 |        |        |        |

#### 2.4.3 Crate Controller Firmware Release

Crate Controller Firmware Release 0x1201 UI1[4] R

This register returns the crate controllers firmware release.

| Access  | CAN-ID | DLC | DATA_ID | Data_3    | Data_2    | Data_1    | Data_0    |

|---------|--------|-----|---------|-----------|-----------|-----------|-----------|

| Request | 0x601  | 2   | 0x1201  |           |           |           |           |

| Answer  | 0x604  | 6   | 0x1201  | Release 1 | Release 2 | Release 3 | Release 4 |

#### 2.4.4 Crate Controller Firmware Name

Crate Controller Firmware Name 0x1203 CHAR[6] R

This register returns the crate controllers firmware name.

| Access  | CAN-ID | DLC | DATA_ID | Data_5 | Data_4 | Data_3 | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|--------|--------|--------|--------|--------|--------|

| Request | 0x601  | 2   | 0x1203  |        |        |        |        |        |        |

| Answer  | 0x604  | 8   | 0x1203  | 'E'    | 'C'    | 'H'    | '4'    | 'x'    | 'A'    |

## 2.4.5 Crate Controller Article Description

Crate Controller Article Description 0x1209 CHAR[] R

This register returns the crate controllers article description. Depending on the length of the article description, multiple CAN messages may be sent. The description is terminated by a zero character.

| Access  | CAN-ID | DLC | DATA_ID | Data_5 | Data_4 | Data_3 | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|--------|--------|--------|--------|--------|--------|

| Request | 0x601  | 2   | 0x1209  |        |        |        |        |        |        |

| Answer  | 0x604  | 38  | 0x1209  | 0      | 'C'    | 'C'    | '2'    | '4'    | 0      |

#### 2.4.6 Crate Controller Control

Crate Controller Control 0x1A01 UI4 R/W

The register Crate Controller Control sets crate functions.

| Access  | CAN-ID | DLC | DATA_ID | Data_3            | Data_2 | Data_1 | Data_0 |  |

|---------|--------|-----|---------|-------------------|--------|--------|--------|--|

| Request | 0x601  | 2   | 0x1A01  |                   |        |        |        |  |

| Answer  | 0x604  | 6   | 0x1A01  | Crate Control UI4 |        |        |        |  |

|         |        |     |         |                   |        |        |        |  |

| Set     | 0x600  | 6   | 0x1A01  | Crate Control U   | 14     |        |        |  |

| Bit31   | Bit30   | Bit29                 | Bit28              | Bit27                   | Bit26                | Bit25                         | Bit24                      |

|---------|---------|-----------------------|--------------------|-------------------------|----------------------|-------------------------------|----------------------------|

| res (0) | res (0) | do Set Legacy<br>Mode | set Legacy<br>Mode | do Set Auto<br>Power On | set Auto<br>Power On | do Set Crate<br>Enable Active | set Crate<br>Enable Active |

| Bit23   | Bit22   | Bit21                 | Bit20              | Bit19                   | Bit18                | Bit17                         | Bit16                      |

| res (0) | res (0) | res (0)               | res (0)            | res (0)                 | res (0)              | res (0)                       | res (0)                    |

| Bit15   | Bit14   | Bit13                 | Bit12              | Bit11                   | Bit10                | Bit09                         | Bit08                      |

| res (0) | res (0) | res (0)               | res (0)            | res (0)                 | res (0)              | res (0)                       | res (0)                    |

| Bit07   | Bit06   | Bit05                 | Bit04              | Bit03                   | Bit02                | Bit01                         | Bit00                      |

| res (0) | res (0) | res (0)               | res (0)            | res (0)                 | res (0)              | do Clear<br>Statistic         | do Clear<br>Events         |

| Status Bit                 | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| do Clear Events            | Clears the crates event status register. This bit can only be written, it always reads zero.                                                                                                                                                                                                                                                                                                |

| doClear Statistic          | Clears the crates statistic registers. This bit can only be written, it always reads zero.                                                                                                                                                                                                                                                                                                  |

| set Crate Enable Active    | If this bit is set to one, the high voltage channels can only be turned on, if the pin Crate Enable at the CONTROL connector is pulled high. This bit can only be changed if the backplane is powered off and the bit do Set Crate Enable Active is set to one.                                                                                                                             |

| do Set Crate Enable Active | This bit masks the bit set Crate Enable Active. If this bit is zero, the bit set Crate Enable Active is ignored. This bit can only be written, it always reads zero.                                                                                                                                                                                                                        |

| set Auto Power On          | If this bit is set to one, the backplane is automatically turned on after the mains line is plugged in. Otherwise, the backplane stays off and must be turned on by the POWER ON switch or by remote control. This bit can only be changed if the bit do Set Auto Power On is set to one.                                                                                                   |

| do Set Auto Power On       | This bit masks the bit set Auto Power On. If this bit is zero, the bit set Auto Power On is ignored. This bit can only be written, it always reads zero.                                                                                                                                                                                                                                    |

| set Legacy Mode            | If this bit is set to one, the controller operates in Legacy Mode. In this mode, the modules can be controlled by CAN bus connected to CAN1 or CAN2. Note that in this mode, the internal services like isegHAL, iCSservice, SNMP, EPICS can not be used to control the modules. This bit can only be changed if the backplane is powered off and the bit do Set Legacy Mode is set to one. |

| do Set Legacy Mode         | This bit masks the bit set Legacy Mode. If this bit is zero, the bit set Legacy Mode is ignored. This bit can only be written, it always reads zero.                                                                                                                                                                                                                                        |

Table 1

## 2.4.7 Crate Controller Status

Crate Controller Status 0x1A00 UI4 R

The Crate Controller Status contains the *actual* status. The bits will be set or reset depending on the crates status.

| Access  | CAN-ID | DLC | DATA_ID | Data_3           | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|------------------|--------|--------|--------|

| Request | 0x601  | 2   | 0x1A00  |                  |        |        |        |

| Answer  | 0x604  | 6   | 0x1A00  | Crate Status UI4 |        |        |        |

| Bit31                | Bit30                | Bit29                | Bit28         | Bit27                   | Bit26                      | Bit25                 | Bit24                 |

|----------------------|----------------------|----------------------|---------------|-------------------------|----------------------------|-----------------------|-----------------------|

| res (0)              | res (0)              | res (0)              | res (0)       | CAN Bus Error<br>Apalis | CAN Bus Error<br>Backplane | CAN Bus Error<br>CAN1 | CAN Bus Error<br>CAN2 |

| Bit23                | Bit22                | Bit21                | Bit20         | Bit19                   | Bit18                      | Bit17                 | Bit16                 |

| res (0)              | res (0)              | Crate Fast Off       | Crate Enabled | Shut Down               | High Voltage<br>On         | Power Fail            | Power On              |

|                      |                      |                      |               |                         |                            |                       |                       |

| Bit15                | Bit14                | Bit13                | Bit12         | Bit11                   | Bit10                      | Bit09                 | Bit08                 |

| <b>Bit15</b> res (0) | <b>Bit14</b> res (0) | <b>Bit13</b> res (0) | Sum Error     | Bit11<br>High +3.3 CC   | <b>Bit10</b> Low +3.3 CC   | Bit09<br>High +5 CC   | Bit08<br>Low +5 CC    |

|                      |                      |                      |               |                         |                            |                       |                       |

| Status Bit              | Description                                                                                                                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAN Bus Error Apalis    | The internal CAN bus between the Crate Controller and the Apalis is in error state                                                                                                                                                         |

| CAN Bus Error Backplane | The internal CAN bus between the Crate Controller and the HV modules is in error state                                                                                                                                                     |

| CAN Bus Error CAN1      | The external CAN bus connected to CAN1 is in error state                                                                                                                                                                                   |

| CAN Bus Error CAN2      | The external CAN bus connected to CAN2 is in error state                                                                                                                                                                                   |

| High-Voltage-On         | Backplane is powered on and at least one channel within the crate has Status.isOn or measured voltage > 63 V The front panel LED HV-ON is derived from this bit.                                                                           |

| Power-On                | Backplane is powered on (modules are supplied with voltage) The front panel LED Status lights green when Power-On is set and no supply error exists. The front panel LED Status lights red when Power-On is set and a supply error exists. |

| Power-Fail              | AC line power fail detected. Crate without UPS: high voltage is turned fast off Crate with UPS: high voltage is turned off with ramp after the wait time                                                                                   |

| High Temperature        | At least one modules or the crate controller have high temperature. The high voltage is turned off with the configured voltage ramp speed.                                                                                                 |

| Shut Down               | If the front button POWER ON is pressed for more than 10 seconds, this bit is set for approx.  1 minute. This is used to perform a shut down of the embedded crate computer.                                                               |

| Sum Error               | This bit is set, whenever one of the bits Power Fail, High Temperature, Service, High Supply, Low Supply or Crate Fast Off is set or if Crate Enabled is cleared.                                                                          |

| Service                 | A fatal error occurred. Contact service.                                                                                                                                                                                                   |

Table 2

| Status Bit     | Description                                                                                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Supply X  | Measured voltage X exceeds the upper limit.                                                                                                                                                                             |

| Low Supply X   | Measured voltage X exceeds the lower limit.                                                                                                                                                                             |

| Crate Enabled  | If the crate is enabled, it is possible to turn on high voltage for all channels. The crate is enabled, if the Crate Control bit set Crate Enable Active is not set, or if the CONTROL pin Crate Enable is pulled high. |

| Crate Fast Off | If the CONTROL pin Crate Fast Off is turned high, the high voltages are shut down without ramp.                                                                                                                         |

#### 2.4.8 Crate Controller Event Status

Crate Controller Event Status 0x1A02 UI4 R/C

The Event Status bits are set together with the status bits. Unlike Status bits, Event Status bits are not reset automatically. The have to be reset by the user, by writing an 1 to this event bit. All Event Status bits are reset by the Crate Control bit do Clear.

| Access  | CAN-ID | DLC | DATA_ID | Data_3                 | Data_2     | Data_1       | Data_0 |  |

|---------|--------|-----|---------|------------------------|------------|--------------|--------|--|

| Request | 0x601  | 2   | 0x1A02  |                        |            |              |        |  |

| Answer  | 0x604  | 6   | 0x1A02  |                        | Crate Even | t Status UI4 |        |  |

|         |        |     |         |                        |            |              |        |  |

| Clear   | 0x600  | 6   | 0x1A02  | Crate Event Status UI4 |            |              |        |  |

| Bit31                | Bit30                | Bit29                | Bit28              | Bit27                     | Bit26                | Bit25               | Bit24              |

|----------------------|----------------------|----------------------|--------------------|---------------------------|----------------------|---------------------|--------------------|

| res (0)              | res (0)              | res (0)              | res (0)            | res (0)                   | res (0)              | res (0)             | res (0)            |

| Bit23                | Bit22                | Bit21                | Bit20              | Bit19                     | Bit18                | Bit17               | Bit16              |

| res (0)              | res (0)              | res (0)              | res (0)            | Shut Down                 | High Voltage<br>On   | Power Fail          | Power On           |

|                      |                      |                      |                    |                           |                      |                     |                    |

| Bit15                | Bit14                | Bit13                | Bit12              | Bit11                     | Bit10                | Bit09               | Bit08              |

| <b>Bit15</b> res (0) | <b>Bit14</b> res (0) | <b>Bit13</b> res (0) | Bit12<br>Sum Error | <b>Bit11</b> High +3.3 CC | Bit10<br>Low +3.3 CC | Bit09<br>High +5 CC | Bit08<br>Low +5 CC |

|                      |                      |                      |                    |                           |                      |                     |                    |

#### 2.4.9 Crate Controller Event Mask

Crate Controller Event Mask 0x1A3 UI4 R/W

The Event Mask is defined for compatibility to the module EDCP command set, but not used at the moment.

| Access  | CAN-ID | DLC | DATA_ID | Data_3 | Data_2     | Data_1      | Data_0 |  |

|---------|--------|-----|---------|--------|------------|-------------|--------|--|

| Request | 0x601  | 2   | 0x1A03  |        |            |             |        |  |

| Answer  | 0x604  | 6   | 0x1A03  |        | Crate Ever | nt Mask UI4 |        |  |

|         |        |     |         |        |            |             |        |  |

| Set     | 0x600  | 6   | 0x1A03  |        | Crate Ever | nt Mask UI4 |        |  |

R

## 2.4.10 Crate Controller Fan Speed Percent

Crate Controller Fan Speed Percent 0x1A04 R4

This register returns the crates fan speed in percent (0...100). The fan speed is regulated according to the maximum crate temperature. The maximum temperature is collected over all modules and the crate controller. The maximum fan speed is reached at approx. 45° C.

| Access  | CAN-ID | DLC | DATA_ID | Data_3             | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|--------------------|--------|--------|--------|

| Request | 0x601  | 2   | 0x1A04  |                    |        |        |        |

| Answer  | 0x604  | 6   | 0x1A04  | Crate Fan Speed R4 |        |        |        |

### 2.4.11 Crate Power On/Off

Crate Power On/Off 0x1A05 UI1 R/W

This register controls the crates power on (1) or off (0) function.

| Access  | CAN-ID | DLC | Data_ID | Data_0 |

|---------|--------|-----|---------|--------|

| Request | 0x601  | 2   | 0x1A05  |        |

| Answer  | 0x604  | 3   | 0x1A05  | 0x00   |

|         |        |     |         |        |

| Set On  | 0x600  | 3   | 0x1A05  | 0x01   |

| Set Off | 0x600  | 3   | 0x1A05  | 0x00   |

#### 2.4.12 Crate Chassis Identification

Crate Controller Chassis Identification 0x1A06 UI6 R

This register contains the 1-Wire serial number that is read from the crate chassis. This number is an unique number for every crate. The six bytes are the 1-Wire serial number without manufacturer code and without CRC.

This register is filled once the backplane was turned on for at least ten seconds.

| Access  | CAN-ID | DLC | DATA_ID | Data_5 | Data_4 | Data_3          | Data_2          | Data_1 | Data_0 |

|---------|--------|-----|---------|--------|--------|-----------------|-----------------|--------|--------|

| Request | 0x601  | 2   | 0x1A06  |        |        |                 |                 |        |        |

| Answer  | 0x604  | 8   | 0x1A06  |        | C      | rate Chassis Id | dentification U | 16     |        |

## 2.4.13 Crate Backplane Type

Crate Backplane Type 0x1A07 UI2 R/C

This register contains the backplane type for the master and all slave crates.

| Access  | CAN-ID | DLC | DATA_ID | Data_1     | Data_0          |

|---------|--------|-----|---------|------------|-----------------|

| Request | 0x601  | 2   | 0x1A07  |            |                 |

| Answer  | 0x604  | 4   | 0x1A07  | Crate Back | kplane Type UI2 |

|         |        |     |         |            |                 |

| Clear   | 0x600  | 2   | 0x1A07  |            |                 |

A write access to this register forces a new scan of the backplane type register. It takes approx. two seconds to scan the system and fill the register again.

| Bit31             | Bit30    | Bit29    | Bit28            | Bit27            | Bit26            | Bit25            | Bit24            |

|-------------------|----------|----------|------------------|------------------|------------------|------------------|------------------|

|                   |          |          |                  |                  |                  |                  |                  |

| Bit23             | Bit22    | Bit21    | Bit20            | Bit19            | Bit18            | Bit17            | Bit16            |

|                   |          |          |                  |                  |                  |                  |                  |

| *                 |          |          |                  |                  |                  |                  |                  |

| Bit15             | Bit14    | Bit13    | Bit12            | Bit11            | Bit10            | Bit09            | Bit08            |

| Bit15<br>Reserved | Reserved | Reserved | Green<br>Slave 5 | Green<br>Slave 4 | Green<br>Slave 3 | Green<br>Slave 2 | Green<br>Slave 1 |

|                   |          |          | Green            | Green            | Green            | Green            | Green            |

| Bit meaning  |                                 |                               |

|--------------|---------------------------------|-------------------------------|

| 0            | Backplane type iseg:            | backplane is sequential       |

| 1            | Backplane type wiener:          | backplane is not sequential   |

| Bit position |                                 |                               |

| 0            | Master crate                    |                               |

| 15           | Slave crates on CAN line yellow | = (1 = Slave 0, 2 = Slave 1,) |

| 812          | Slave crates on CAN line green  | = (8 = Slave 0, 9 = Slave 1,) |

### 2.4.14 Crate Temperature Sensor

Crate Temperature Sensor 0x2001 R4 R

This register contains the actual temperature for different sensors.

Sensor 0 and 1 are placed at the crate controller. Sensor 2 is the maximum temperature in the crate (collected over all modules and the crate controller). The maximum temperature is used to control the crates fan speeds.

If the request is done with DLC = 2, all temperature sensors are returned in three CAN messages. If the request is done with DLC = 3 and a specific sensor, only this sensor is returned.

| Access  | CAN-ID | DLC | DATA_ID | Sensor | Data_3 | Data_2                 | Data_1         | Data_0 |  |

|---------|--------|-----|---------|--------|--------|------------------------|----------------|--------|--|

| Request | 0x601  | 2   | 0x2001  |        |        |                        |                |        |  |

| Answer  | 0x604  | 7   | 0x2001  | 0x00   |        | Crate Temperature 0 R4 |                |        |  |

|         | 0x604  | 7   | 0x2001  | 0x01   |        | Crate Temperature 1 R4 |                |        |  |

|         | 0x604  | 7   | 0x2001  | 0x02   |        | Crate Ten              | nperature 2 R4 |        |  |

|         |        |     |         |        | '      |                        |                |        |  |

| Request | 0x601  | 3   | 0x2001  | 0x01   |        |                        |                |        |  |

| Answer  | 0x604  | 7   | 0x2001  | 0x01   |        | Crate Ten              | nperature 0 R4 |        |  |

## 2.4.15 Crate Supply Measurement

Crate Supply Measurement 0x2002 R4 R

This register contains the measured supply voltages.

If the request is done with DLC = 2, all supply measurement values are returned in consecutive CAN messages. If the request is done with DLC = 3 and a specific supply number, only this measurement value is returned.

| Access  | CAN-ID | DLC | DATA_ID | Supply | Data_3 | Data_2                        | Data_1      | Data_0 |  |

|---------|--------|-----|---------|--------|--------|-------------------------------|-------------|--------|--|

| Request | 0x601  | 2   | 0x2002  |        |        |                               |             |        |  |

| Answer  | 0x604  | 7   | 0x2002  | 0x00   |        | Crate Supply Measurement 0 R4 |             |        |  |

|         | 0x604  | 7   | 0x2002  | 0x01   |        |                               |             |        |  |

|         | 0x604  | 7   | 0x2002  | 0x08   |        | Crate Supply                  | Measurement | 8 R4   |  |

### 2.4.16 Crate Supply Nominal

Crate Supply Nominal 0x2003 R4 R

This register contains the nominal supply voltages.

If the request is done with DLC = 2, all supply nominal values are returned in consecutive CAN messages. If the request is done with DLC = 3 and a specific supply number, only this nominal value is returned.

| Access  | CAN-ID | DLC | DATA_ID | Supply | Data_3                    | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|--------|---------------------------|--------|--------|--------|

| Request | 0x601  | 2   | 0x2003  |        |                           |        |        |        |

| Answer  | 0x604  | 7   | 0x2003  | 0x00   | Crate Supply Nominal 0 R4 |        |        |        |

|         | 0x604  | 7   | 0x2003  | 0x01   |                           |        |        |        |

|         | 0x604  | 7   | 0x2003  | 0x08   | Crate Supply Nominal 8 R4 |        |        |        |

## 2.5 Statistic registers

For each CAN bus, multiple statistic registers are kept. The Crate Controller owns four CAN busses, which are numbered the following way:

- 0) CAN PC

- 1) CAN Backplane

- 2) CAN 2

- 3) CAN 1

The existing statistic registers are described below.

If a request message without a CAN bus number (DLC = 2) is received, the statistic register for all four CAN busses are returned.

The statistic counter are incremented by the crate controller and can be reset by the NMT command NMT\_CAN\_RESET together with the CAN interfaces or by the Crate Control bit do Clear Statistic.

#### 2.5.1 CAN Bus Received

CAN Bus Received 0x2040 UI4 R

This register counts the received messages for the given CAN bus.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3 | Data_2     | Data_1      | Data_0 |

|---------|--------|-----|---------|---------|--------|------------|-------------|--------|

| Request | 0x601  | 3   | 0x2040  | 00      |        |            |             |        |

| Answer  | 0x604  | 7   | 0x2040  | 00      |        | Received M | essages UI4 |        |

#### 2.5.2 CAN Bus Receiver Overrun

CAN Bus Receiver Overrun 0x2041 UI4 R

This register counts the receive buffer overruns for the given CAN bus. A receive buffer overrun occurs, if a CAN message could not be read in time from the CAN bus.

This register should always be zero.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3                        | Data_2 | Data_1 | Data_0 |

|---------|--------|-----|---------|---------|-------------------------------|--------|--------|--------|

| Request | 0x601  | 3   | 0x2041  | 00      |                               |        |        |        |

| Answer  | 0x604  | 7   | 0x2041  | 00      | Receiver Overrun Messages UI4 |        |        | 14     |

#### 2.5.3 CAN Bus Transmitted

CAN Bus Transmitted 0x2042 UI4 R

This register counts the transmitted messages for the given CAN bus.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3 | Data_2      | Data_1       | Data_0 |

|---------|--------|-----|---------|---------|--------|-------------|--------------|--------|

| Request | 0x601  | 3   | 0x2042  | 00      |        |             |              |        |

| Answer  | 0x604  | 7   | 0x2042  | 00      |        | Transmitted | Messages UI4 |        |

## 2.5.4 CAN Bus Transmit Buffer Full

CAN Bus Transmit Buffer Full 0x2043 UI4 R

This register counts the messages, that could not be sent to the given CAN bus because of full transmit buffer.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3 | Data_2      | Data_1         | Data_0 |

|---------|--------|-----|---------|---------|--------|-------------|----------------|--------|

| Request | 0x601  | 3   | 0x2043  | 00      |        |             |                |        |

| Answer  | 0x604  | 7   | 0x2043  | 00      |        | Transmit Bu | uffer Full UI4 |        |

## 2.5.5 CAN Bus Dropped

CAN Bus Dropped 0x2044 UI4 R

This register counts the messages that were received from the given CAN bus and could not be routed because of unclear destination.

This register should always be zero.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3 | Data_2    | Data_1      | Data_0 |

|---------|--------|-----|---------|---------|--------|-----------|-------------|--------|

| Request | 0x601  | 3   | 0x2044  | 00      |        |           |             |        |

| Answer  | 0x604  | 7   | 0x2044  | 00      |        | Dropped M | essages UI4 |        |

### 2.5.6 CAN Bus Error

CAN Bus Error 0x2045 UI4 R

This register is incremented every second when the given CAN bus is in error state.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3 | Data_2    | Data_1   | Data_0 |

|---------|--------|-----|---------|---------|--------|-----------|----------|--------|

| Request | 0x601  | 3   | 0x2045  | 00      |        |           |          |        |

| Answer  | 0x604  | 7   | 0x2045  | 00      |        | Error Sec | onds UI4 |        |

#### 2.5.7 CAN Bus Throttle

CAN Bus Throttle 0x2046 UI4 R

This register counts the number of generated throttle messages for the given CAN bus.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3                | Data_2 | Data_1 | Data_0 |  |

|---------|--------|-----|---------|---------|-----------------------|--------|--------|--------|--|

| Request | 0x601  | 3   | 0x2046  | 00      |                       |        |        |        |  |

| Answer  | 0x604  | 7   | 0x2046  | 00      | Throttle Messages UI4 |        |        |        |  |

#### 2.5.8 CAN Bus Status

CAN Bus Status 0x2047 UI4 R

This register holds the current status for the given CAN bus.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3         | Data_2 | Data_1 | Data_0 |  |

|---------|--------|-----|---------|---------|----------------|--------|--------|--------|--|

| Request | 0x601  | 3   | 0x2047  | 00      | 1              | 2      | 3      | 4      |  |

| Answer  | 0x604  | 7   | 0x2047  | 00      | Bus Status UI4 |        |        |        |  |

The CAN Bus Status register contains the following information:

- Receiver bus status: Ok (0), Warning (1), Error (2), Bus off (3)

- Transmitter bus status: Ok (0), Warning (1), Error (2), Bus off (3)

- CAN hardware activated

- CAN hardware synchronized with CAN bus

- CAN hardware in special mode (initializing, sleep, listen-only, loopback).

These bits should not be set in normal operation conditions.

The CAN hardware status is refreshed at the time of the request.

| Bit31 | Bit30 | Bit29          | Bit28             | Bit27            | Bit26             | Bit25    | Bit24        |

|-------|-------|----------------|-------------------|------------------|-------------------|----------|--------------|

|       |       |                |                   |                  |                   |          |              |

| Bit23 | Bit22 | Bit21          | Bit20             | Bit19            | Bit18             | Bit17    | Bit16        |

|       |       | Loopback       | Listen Only       | Enabled          | Synchronized      | Sleeping | Initializing |

| Bit15 | Bit14 | Bit13          | Bit12             | Bit11            | Bit10             | Bit09    | Bit08        |

|       |       | Transmitter bu | s status (0 = Ok, | 1 = Warning, 2 = | Error, 3 = Bus of | f)       |              |

| Bit07 | Bit06 | Bit05          | Bit04             | Bit03            | Bit02             | Bit01    | Bit00        |

| Dicor | Dicoo |                | status (0 = Ok, 1 |                  |                   | Bicor    | Bittoo       |

|       |       |                |                   |                  | ,                 |          |              |

#### 2.5.9 CAN Bus Disabled

CAN Bus Disabled 0x2048 UI4 R

This register counts the number of dropped messages because the given CAN bus is not enabled (e.g. backplane is off).

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3                | Data_2 | Data_1 | Data_0 |  |

|---------|--------|-----|---------|---------|-----------------------|--------|--------|--------|--|

| Request | 0x601  | 3   | 0x2048  | 00      |                       |        |        |        |  |

| Answer  | 0x604  | 7   | 0x2048  | 00      | Disabled Messages UI4 |        |        |        |  |

#### 2.5.10 CAN Bus Bitrate

CAN Bus Bitrate 0x2049 UI4 R

This register holds the current bit rate for the given CAN bus.

| Access  | CAN-ID | DLC | DATA_ID | CAN bus | Data_3      | Data_2 | Data_1 | Data_0 |  |

|---------|--------|-----|---------|---------|-------------|--------|--------|--------|--|

| Request | 0x601  | 3   | 0x2049  | 00      |             |        |        |        |  |

| Answer  | 0x604  | 7   | 0x2049  | 00      | Bitrate UI4 |        |        |        |  |

## 2.6 Examples

CC = Crate-Controller, PC = Controlling PC

| Message             | Direction | CAN-ID | DLC | Data ID | Data | Data | Data | Data |

|---------------------|-----------|--------|-----|---------|------|------|------|------|

| Log-On Request      | CC → PC   | 601    | 3   | D8 00   | 2E   |      |      |      |

| Log-On Confirmation | CC → PC   | 600    | 2   | D8 01   |      |      |      |      |

| Status Request      | PC → CC   | 601    | 2   | 1A 00   |      |      |      |      |

| Status Answer       | CC → PC   | 604    | 6   | 1A 00   | 00   | 00   | 00   | 00   |

| Crate Power On      | PC → CC   | 600    | 3   | 1A 05   | 01   |      |      |      |

| Crate Power Off     | PC → CC   | 600    | 3   | 1A 05   | 00   |      |      |      |

| Fan Speed Request   | PC → CC   | 601    | 2   | 1A 04   |      |      |      |      |

| Fan Speed Answer    | CC → PC   | 604    | 6   | 1A 04   | 40   | A0   | 00   | 00   |

Table 3

Request Temperatures and Supplies (group request)

| Message                          | CAN-ID | DLC | DataID | Channel | Data | Data | Data | Data | Value   |

|----------------------------------|--------|-----|--------|---------|------|------|------|------|---------|

| Request all<br>Temperatures      | 601    | 2   | 20 01  |         |      |      |      |      |         |

| Temperature 0                    | 604    | 7   | 20 01  | 00      | 41   | EF   | 0D   | В0   | 29.9 °C |

| Temperature 1                    | 604    | 7   | 20 01  | 01      | 41   | ED   | 66   | 30   | 29.7 °C |

| Temperature 2                    | 604    | 7   | 20 01  | 02      | 41   | EF   | 0D   | В0   | 29.9 °C |

| Request all Measured<br>Supplies | 601    | 2   | 20 02  |         |      |      |      |      |         |

| Backplane +24                    | 604    | 7   | 20 02  | 00      | 41   | BE   | 75   | 98   | 23,8 V  |

| Reserved                         | 604    | 7   | 20 02  | 01      | 00   | 00   | 00   | 00   | 0 (res) |

| Backplane +5                     | 604    | 7   | 20 02  | 02      | 40   | A0   | 51   | EC   | 5,01 V  |

| Reserved                         | 604    | 7   | 20 02  | 03      | 00   | 00   | 00   | 00   | 0 (res) |

| Reserved                         | 604    | 7   | 20 02  | 04      | 00   | 00   | 00   | 00   | 0 (res) |

| Supply +5                        | 604    | 7   | 20 02  | 05      | 40   | 9F   | A2   | 1B   | 4,99 V  |

| Supply +3.3                      | 604    | 7   | 20 02  | 06      | 40   | 53   | 2E   | 1C   | 2,99 V  |

| Reserved                         | 604    | 7   | 20 02  | 07      | 00   | 00   | 00   | 00   | 0 (res) |

| Battery + 24                     | 604    | 7   | 20 02  | 08      | 41   | D0   | СС   | CD   | 26,1 V  |

Table 4

## 3 Commands for High Voltage Devices

## 3.1 General information

Each single HV channel is independently controllable. The modules are software controlled via CAN-Interface through a PC or similar controller.

Using an iseg crate combined with a CC24 controller or an iCSmini as stand alone iseg Communication Server WEB-services, Remote-service, EPICS and SNMP are possible via Ethernet.